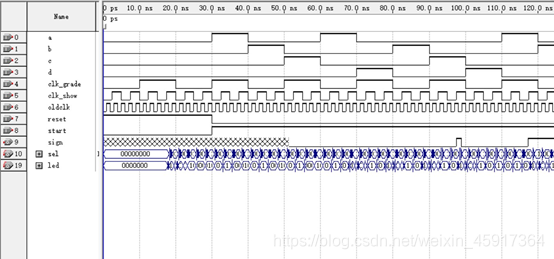

1. 设计并实现一个随机数生成电路,每2秒随机生成一个0~999之间的数字,并在数码管上显示生成的随机数。2. 为系统设置一个复位键,复位后数码管显示“000”,2秒后再开始每2秒生成并显示随机数,要求使用按键复位。

”quartus随机数 vhdl 随机数生成器 随机数电路 随机数“ 的搜索结果

北邮数电实验 6 随机数生成电路的设计与实现 报告(含VHDL代码)

该文件是完整工程的代码,请用Quartus打开,还有该代码的数电EDA实验报告请看我上传的文件

(rand()&0xFFF|(rand()&0xFFF)可以这样得到 0 - 999999 之间的随机数

通过EN开关来控制整个程序,EN为0时显示学号,为1时开始运行程序。... 整个程序由八个主要模块组成:分频模块,随机数产生模块, 比较模块,数码管显示模块,计分模块,历史记录模块和倒计时模块。

书写testbench是数字电路设计中不可或缺的一项设计方法,主要是提供的是激励。尽管现在各种开发工具都通过绘制波形图的方法生成测试激励,测试书写的代码,但是其不可移植性,不可通用性,还有有些功能无法是实现,...

利用VHDL实现VGA控制器,显示地球和月球图形。再利用quartus12.0中的SOC NIOSII系统产生随机数,使得地球随机运动而月球跟随地球转动。

Verilog HDL 是一种硬件描述语言,以...代码编写完成之后使用我们前面安装的 Quartus II 开发软件对 Verilog HDL 语言编写的代码进行一个分析综合、布局布线等一系列操作,然后将生成的网表文件下载到 FPGA 开发板中

但是下载到板子(EMP1270144c5)上后却不按要求显示初始“爱心欢迎界面”,而是显示S1的内容,并且点阵内容显示不完整(只显示第一行的)、数码管虽然显示了随机数但是每秒就更换一次随机数。 按rst键会出现开始的...

书写testbench是数字电路设计中不可或缺的一项设计方法,主要是提供的是激励。尽管现在各种开发工具都通过绘制波形图的方法生成测试激励,测试书写的代码,但是其不可移植性,不可通用性,还有有些功能无法是实现,...

硬件电路设计和C语言程序设计有着本实上的区别。各位大侠可依据自己的需要进行阅读,参考学习。 第二篇内容摘要:本篇介绍系统的 verilog 实现。根据个人的设计经验,在硬件设计中,以整个系统...

第2章 设计语言及环境介绍

语音合成:把语音波形文件重现,以一种灵活的方式,只用极少数的基础数据,比如元音辅音的语音参数,那么首先需要研究元音辅音的语音学性质。 先从元音开始,根据相关资料,不同的元音是由相同的原始声带音通过不同...

尽管现在各种开发工具都通过绘制波形图的方法生成测试激励,测试书写的代码,但是其不可移植性,不可通用性,还有有些功能无法是实现,如监视变量的值的变化,显示数据的状态等。 一个完整的testbench包含下列几...

DSP Builder是Altera推出的一个数字信号处理(DSP)开发工具,它在Quartus Ⅱ FPGA设计环境中集成了MathWorks的Matlab和Simulink DSP开发软件。Altera的DSP系统体系解决方案是一项具有开创性的解决方案,它将FPGA的...

推荐计算机科学类的经典书籍(一)1.The Art of Computer ProgrammingAuthor: Donald.E.Knuth Web site: http://www-cs-faculty.stanford.edu/~knuth/taocp.html Book Info: 这部书被誉为20世纪最重要的20部著作之一...

推荐文章

- 机器学习之超参数优化 - 网格优化方法(随机网格搜索)_网格搜索参数优化-程序员宅基地

- Lumina网络进入SDN市场-程序员宅基地

- python引用传递的区别_php传值引用的区别-程序员宅基地

- 《TCP/IP详解 卷2》 笔记: 简介_tcpip详解卷二有必要看吗-程序员宅基地

- 饺子播放器Jzvd使用过程中遇到的问题汇总-程序员宅基地

- python- flask current_app详解,与 current_app._get_current_object()的区别以及异步发送邮件实例-程序员宅基地

- 堪比ps的mac修图软件 Pixelmator Pro 2.0.6中文版 支持Silicon M1_pixelmator堆栈-程序员宅基地

- 「USACO2015」 最大流 - 树上差分_usaco 差分-程序员宅基地

- Leetcode #315: 计算右侧小于当前元素的个数_找元素右边比他小的数字-程序员宅基地

- HTTP图解读书笔记(第六章 HTTP首部)响应首部字段_web响应的首部内容-程序员宅基地